片上总线Wishbone 学习(十二)总线周期之块写操作

异步周期结束方式

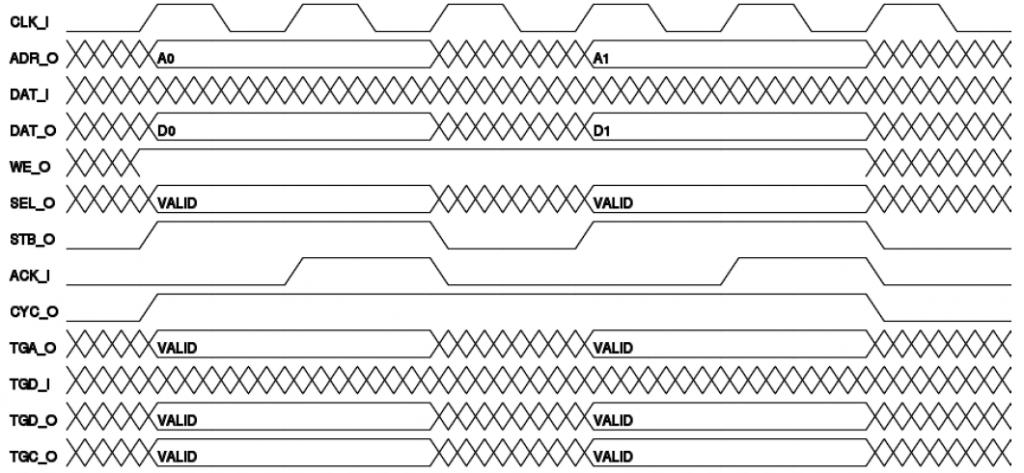

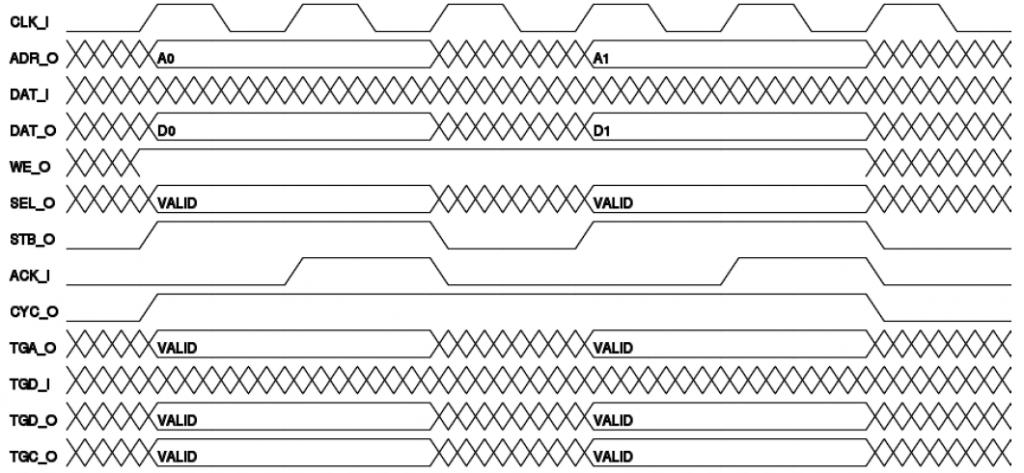

块写操作的例子如图1所示。图1的一次块写操作由五个相互关联的单次写操作完成。

在时钟上升沿0,主设备将地址信号ADR_O()、TGA_O()放到总线上,将数据信号DAT_O()、TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作正在进行,将STB_O置高表示第一次写操作开始。

在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿1,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第一次写操作完成,于是将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作继续在进行,将STB_O置高表示第二次写操作开始。

在时钟上升沿2到达之前,从设备检测到主设备发起的第二次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿2,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第二次写操作完成,发现自己的数据还没有准备好,于是将STB_O置低表示插入等待周期。

在时钟上升沿3到达之前,从设备检测到STB_O为低,也将ACK_I置低。

在时钟上升沿3,主设备发起第三次操作,将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将WE_O置为高表示写操作,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将CYC_O和TGC_O置高表示操作继续进行,将STB_O置高表示第三次写操作开始。

在时钟上升沿4到达之前,从设备检测到主设备发起的第三次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿4,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第三次写操作完成,于是将新地址信号ADR_O()、新TGA_O()放到总线上,将新数据信号DAT_O()、新TGD_O()放到总线上,将适当的SEL_O()信号置高通知从设备将数据总线上哪些信号是有效的,将STB_O继续置高表示第四次写操作开始。

在时钟上升沿5到达之前,从设备检测到主设备发起的第四次写操作,将主设备的ACK_I置高作为对主设备STB_O的响应。

在时钟上升沿5,从设备将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第四次写操作完成,于是发起第五次操作,将新地址信号ADR_O()、新TGA_O()放到总线上。

在时钟上升沿5之后新的时钟上升沿到达之前,从设备发现因为某些原因暂时无法继续接收数据,因此将ACK_I信号置低,插入等待。

在时钟上升沿6,当从设备发现可以继续接收数据,于是在在最后一个等待周期结束且上升沿5到达之前,将DAT_I()和TGD_I()采样;主设备发现ACK_I信号为高,得知第五次写操作完成。并将STB_O和CYC_O置低表示整个块写操作完成。

图1 Wishbone总线的块写操作(异步周期结束方式)

同步周期结束方式

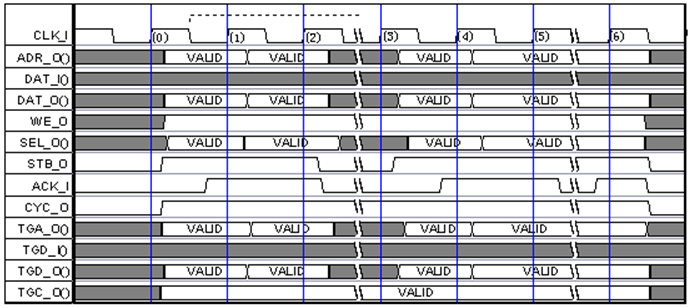

图2 Wishbone总线的块写操作(同步周期结束方式)

在时钟上升沿0:

- Master在[ADR_O()]和[TGA_O()]发出有效的地址

- Master在[DAT_O()]和[TGD_O()]发出数据

- Master发出[WE_O],表明是一个写周期

- Master发出有效数据选择信号[SEL_O()]表明哪些数据是有效的

- Master发出[CYC_O]和[TGC_O()]表明总线周期的开始

- Master发出[STB_O]表明操作的开始

注意:Mater必须在时钟上升沿1或之前发出[CYC_O]和/或[TGC_O()]

在时钟上升沿1:

- Slave检测到主设备发起的操作,准备发出[ACK_I]

- Slave准备锁存[DAT_O]和[TGD_O()]

- Slave发出[ACK_I]应答[STB_O]

在时钟上升沿2:

- Slave锁存[DAT_I]和[TGD_I()]

- Master拉低[STB_O]插入等待周期(-WSS-)

在时钟上升沿3:

- Master在[ADR_O()]和[TGA_O()]发出有效的地址

- Master在[DAT_O()]和[TGD_O()]发出数据

- Master发出[WE_O],表明是一个写周期

- Master发出有效数据选择信号[SEL_O()]表明哪些数据是有效的

- Master发出[CYC_O]和[TGC_O()]表明总线周期的开始

- Master发出[STB_O]表明第二次操作的开始

在时钟上升沿4:

- Slave检测到主设备发起的操作,准备发出[ACK_I]

- Slave准备锁存[DAT_O]和[TGD_O()]

在时钟上升沿5:

- Master监视[ACK_I]

- Master拉低[STB_O]和[CYC_O],结束总线周期

分享到:

相关推荐

wishbone总线是一种免费开放的总线协议,被大多数芯片厂商采用。

Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线

wishbone总线规范第3版,常用的片上总线

目前使用最多的三个总线协议:axi, ocp, wishbone. 本文是wishbone协议部分

wishbone总线信号接口详解,相信对你很有帮助

WISHBONE总线协议下DDR存储控制器设计

流片验证过的wishbone接口的 I2C总线 verilog 代码

WISHBONE System-on-Chip (SoC)Interconnection Architecturefor Portable IP Cores Copyright Notice:This ebook is Copyright © 2010 OpenCores Wishbone最新版协议

基于FPGA的SDX总线与Wishbone总线接口设计.pdf

wishbone总线入门介绍,通俗易懂,可以作为wishbone入门的资料

很详细的WB总线协议、接口、时序讲解,并且有部分设计实例的代码。

关于soc系统总线的描述:在基于臻复】I...本文介绍丁目前SoC设计中常用的五种片上总线标准,即CoreConnect总线、AMBA总线、Avalon总线、Wishbone 总线和OCP总线,分析和比较了它们的特性,并在此基础上阐述其应用领域。

绍了一种基于Wishbone总线的UART IP核的设计方法。该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果...

Wishbone总线接口在以太网控制器IP核中的应用,郑拓,张荐,对于可移植IP核,Wishbone 片上系统互连结构是一种灵活的设计方法。利用Wishbone总线进行的互连通过建立一种标准的数据交换协议和通用��

wishbone总线协议中文版,五十多页内容非常丰富,基本上用到的都有,包括读写时序等。

对于了解认识 wishone 总线协议的朋友们来说很值得一看

用SPI总线驱动Wishbone主总线。 协议 如下: 模式b01-> CPOL = 0 CPHA = 1 CS =低电平有效 spi2wb帧的组成如下: 8位模式 写框: MOSI : 1AAAAAAA DDDDDDDD MISO : ZZZZZZZZ ZZZZZZZZ 读框 MOSI : 0AAAAAAA ...

Nor flash controller源代码和文档说明,wishbone总线接口的

摘要:讨论了PCI主桥的应用和Wishbone片上总线技术,详细介绍了基于Wishbone总线的PCI Bridge核的功能、内部结构和操作方式。实验证明,在PCI系统中使用PCI Bridge核进行开发设计,电路简洁,使用方便灵活。 ...