片上总线Wishbone 学习(七)总线周期之握手协议

由于在整个总线周期,CYC_O必须始终保持有效,因此,此后我们将在给出的图中忽略该信号,只在必要的时候给出。

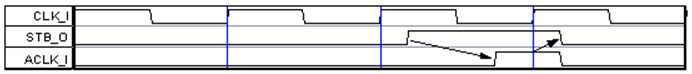

握手发生在主设备和从设备之间。握手协议是主设备和从设备在握手时所遵守的共同规则。如图6,当主设备准备好,它将STB_O信号置高。STB_O信号一直为高,直到从设备通过置高ACK_O、ERR_O、RTY_O对本次操作发起响应。在图7中我们以主设备的ACK_I信号作为示例,后文也如此。通过握手,主设备和从设备不仅可以完成通信,而且可以控制它们之间的通信速率。

图1Wishbone总线的基本握手协议

如果从设备保证能够在主设备发起操作时及时作出操作成功的响应,其ACK_O信号可以设计为STB_I和CYC_I信号的逻辑与,而ERR_O和RTY_O信号也可以不使用。因此ERR_O和RTY_O信号是可选的,而ACK_O信号是必须的。在点对点连接中,甚至可以将ACK_I信号直接置高。当存在ERR_O和RTY_O信号,主设备当发现ERR_O和RTY_O信号之一有效时如何进行响应取决于主设备的设计。

对于从设备,只有STB_I和CYC_I同时为高时,才能发起对主设备的响应。

实际上,对于主设备,其最小配置为只有ACK_I、CLK_I、CYC_O、RST_I和STB_O;而对于从设备,其最小配置为只有ACK_O、CLK_I、CYC_I、RST_I和STB_I,这里CYC和STB信号可以合并到一起成为一个信号,通常命名为CYCSTB_O/。

在图1中,从STB_O到ACK_I存在一个长组合逻辑路径,在实际系统中很可能成为关键路径。因此,在设计中应尽量保证STB_O是触发器的直接输出。如果从STB_O到ACK_I存在一个长组合逻辑路径延迟不能满足设计的时序要求,可将从设备的ACK_O经过触发器寄存后再输出,从而将长组合逻辑打破,但系统的吞吐量也将因此减小。关于如何即打破长组合逻辑又不影响系统的吞吐量,以后的文章将进行详细讨论。

分享到:

相关推荐

wishbone总线是一种免费开放的总线协议,被大多数芯片厂商采用。

WISHBONE总线协议下DDR存储控制器设计

WISHBONE System-on-Chip (SoC)Interconnection Architecturefor Portable IP Cores Copyright Notice:This ebook is Copyright © 2010 OpenCores Wishbone最新版协议

目前使用最多的三个总线协议:axi, ocp, wishbone. 本文是wishbone协议部分

Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线 Wishbone总线

wishbone总线规范第3版,常用的片上总线

基于FPGA的SDX总线与Wishbone总线接口设计.pdf

wishbone总线协议中文版,五十多页内容非常丰富,基本上用到的都有,包括读写时序等。

wishbone协议中文版.docx

Wishbone B4协议 Wishbone B4协议 Wishbone B4协议 Wishbone B4协议 Wishbone B4协议

wishbone总线信号接口详解,相信对你很有帮助

流片验证过的wishbone接口的 I2C总线 verilog 代码

很详细的WB总线协议、接口、时序讲解,并且有部分设计实例的代码。

wishbone总线入门介绍,通俗易懂,可以作为wishbone入门的资料

关于soc系统总线的描述:在基于臻复】I...本文介绍丁目前SoC设计中常用的五种片上总线标准,即CoreConnect总线、AMBA总线、Avalon总线、Wishbone 总线和OCP总线,分析和比较了它们的特性,并在此基础上阐述其应用领域。

Wishbone总线接口在以太网控制器IP核中的应用,郑拓,张荐,对于可移植IP核,Wishbone 片上系统互连结构是一种灵活的设计方法。利用Wishbone总线进行的互连通过建立一种标准的数据交换协议和通用��

绍了一种基于Wishbone总线的UART IP核的设计方法。该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果...

对于了解认识 wishone 总线协议的朋友们来说很值得一看

基于Wishbone片上总线的PCI Bridge核的研究和应 [日期:2005-8-8] 来源:国外电子元器件 作者:徐江丰 李 松 张 涌 [字体:大 中 小] 摘要:讨论了PCI主桥的应用和Wishbone片上总线技术,详细介绍...