- 浏览: 6177161 次

-

最新评论

-

vb2005xu:

这样你跑一个1000试试,卡不死你

PHP实现斐波那契数列 -

ykbj117:

你们知道刘绍华么?就是北邮的一个教授,专门研究WebRTC的资 ...

WebRTC体系结构 -

huangbye:

其实这也没什么卵用!

thinkphp自定义标签,view直接标签连接数据 -

cofftech:

opencv源码:http://www.eyesourceco ...

opencv资料和文档 -

langke93:

wangzhengyi_nopass.key这个怎么生成没写

nginx搭建https服务器

相关推荐

2 本设计支持 I2S 左对齐 右对齐格式的 I2S 协议以及 S PDIF 协议等多种音频协 议" 3 设计可配置:时钟和帧同步及其极性可配置;数据格式可配置;帧内时间槽长可 配置可为七种类型之一;槽内的有效数据的字长可...

I2S(Inter—IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,...

通过在FPGA中将PCI软核、FIFO以及设计的接口电路等相结合,在FPGA上实现了 PCI、I2C、I2S等多种总线,并且结合音频解码器实现了不同采样频率语音数据的传输以及播放功能。系统充分利用FPGA的片上资源及其可编程特性...

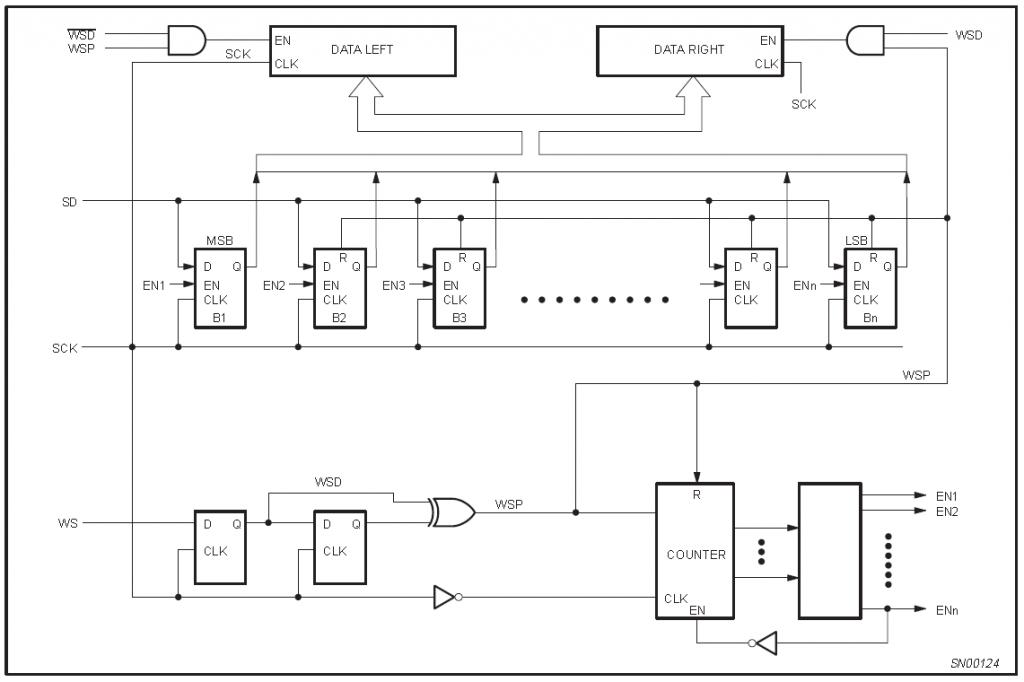

I2S(Inter IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,它既规定了硬件接口规范,也规定了数字音频数据的格式。I2S有三个主要的信号: (1)串行时钟BCLK,也叫位时钟...

但是在嵌入式音频系统设计中,并不是所有的MCU都支持I2S总线格式,再加上I2S还没有统一的接口标准,不同的厂家生产的设备接口也是五花八门,采用软件模拟实现I2S总线可有效解决在不支持其的MCU和设备之间通过I2S总线...

I2S(Inter IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,它既规定了硬件接口规范,也规定了数字音频数据的格式。I2S有三个主要的信号: (1)串行时钟BCLK,也叫位时钟...

I2S(Inter—IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,...

音频编解码:ES7243E 支持多种音频编解码格式,包括 PCM(脉冲编码调制)、I2S(串行音频接口)、SPDIF(Sony/Philips数字接口)等。它可以将音频信号进行编码和解码,以实现音频数据的传输和处理。 高音质和低噪声...

6.6.3 S3C2410A的I2S总线接口 6.6.4 I2S总线接口电路与编程 思考题与习题 第7章 嵌入式系统网络接口 7.1以太网接口 7.1.1 以太网基础知识 7.1.2 嵌入式以太网接口的实现方法 7.1.3 在嵌入式系统中主要处理的以太网...

二、AG9311特点1、显示AG9311符合DisplayPort specification Revision 1.2AG9311支持1.62(RBR)/2.7(HBR)/5.4(HBR2)Gbps数据速率支持1/2线路配置支持下行扩频时钟(SSC)AG9311支持I2S总线音频提取2、HDMIHDMI...

基于8051单片机的1553B总线接口设计.pdf 基于8051单片机的双通道波形发生器的设计与实现.pdf 基于8051单片机的新型微波开关矩阵.pdf 基于8051单片机的温度采集系统.pdf 基于80C196KC单片机的任意波形发生器的设计....

IIS 总线音频编码器接口 ● AC’97 编解码器接口 ● 兼容 SD 主接口协议 1.0 版和 MMC 卡协议 2.11 兼容版 ● 2 通道 USB 主机/1 通道 USB 设备(1.1 版) ● 4 通道 PWM 定时器和 1 通道内部定时器/看门狗定时器 ●...

可用的外设包括符合BT 656 标准的相机接口、三个全双工IIS音频通道、一个AC97接口、一个内置式2通道16位音频流DAC、一个以太网MAC、一个带7个端点的高速 (480Mb/s) USB设备接口、一个双端口MMC/SD卡接口、四个USART...

1788开发板是广州致远电子股份有限公司精心设计的一款集教学、竞赛、实验于一身的开发套件,套件以NXP公司的LPC1788为核心,该芯片具有EMC(外部总线接口),支持SDRAM和NOR Flash扩展,并提供5路串口、1路10/100M...

神经元芯片(neuron chip)是lon works技术的核心所在,它是一个带有多个处理器、读写/只读存储器(ram/rom)以及通 信和i/o接口的单芯片系统。只读存储器包含一个操作系统、lon talk协议和1/0功能库。neuron c是一...

飞利浦基于SAA7160E PCI Express的音频/视频桥接为视频图像捕捉、节目/传输和音频流提供了所需的端口,包括两个最多可支持4个频道的I2S-总线输入端口,用于实现高质量的音频功能。SAA7162E利用PCI Express桥接

很难给这个设计方案定义一个...除具备一般嵌入式芯片所具有的总线,SDRAM控制器,3个串口等外设之外,S3C2410还具有TFT LCD控制器、USB Slave、USB Host、I2C总线控制器、SPI控制器、IIS音频接口、SD & MMC存储卡接口

很难给这个设计方案定义一个确切的...除具备一般嵌入式芯片所具有的总线,SDRAM控制器,3个串口等外设之外,S3C2410还具有TFT LCD控制器、USB Slave、USB Host、I2C总线控制器、SPI控制器、IIS音频接口、SD & MMC存储卡

用户线接口电路 二/ 四线变换器 二/四线变换器 用户线接口电路 用户1 PCM CODEC电路 PCM CODEC电路 用户3 用户线接口电路 二/ 四线变换器 二/ 四线变换器 用户线接口电路 用户2 PCM CODEC电路 PCM CODEC电路 ...