详解SPI中的极性CPOL和相位CPHA

SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

(2) CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

(3) SCK=SCLK=SPI的时钟

(4) Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)

对于一个时钟周期内,有两个edge,分别称为:

(1)Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

(2)Trailing edge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

本博文采用如下用法:

- 极性=CPOL

- 相位=CPHA

- SCLK=时钟

- 第一个边沿和第二个边沿

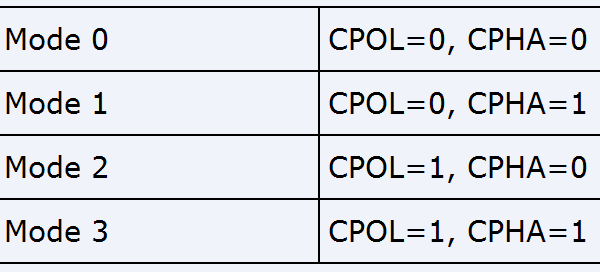

CPOL和CPHA,分别都可以是0或时1,对应的四种组合就是:

下面详细介绍。

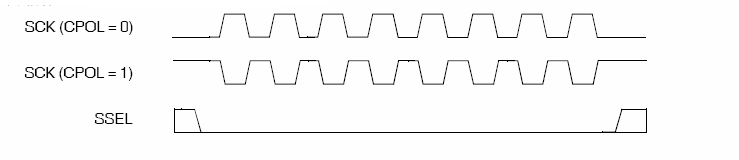

CPOL极性

先说什么是SCLK时钟的空闲时刻,其就是当SCLK在发送8个bit比特数据之前和之后的状态,于此对应的,SCLK在发送数据的时候,就是正常的工作的时候,有效active的时刻了。其英文精简解释为:Clock Polarity = IDLE state of SCK。

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:

CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high;

CPOL=1,时钟空闲idle时候的电平是高电平,所以当SCLK有效的时候,就是低电平,就是所谓的active-low;

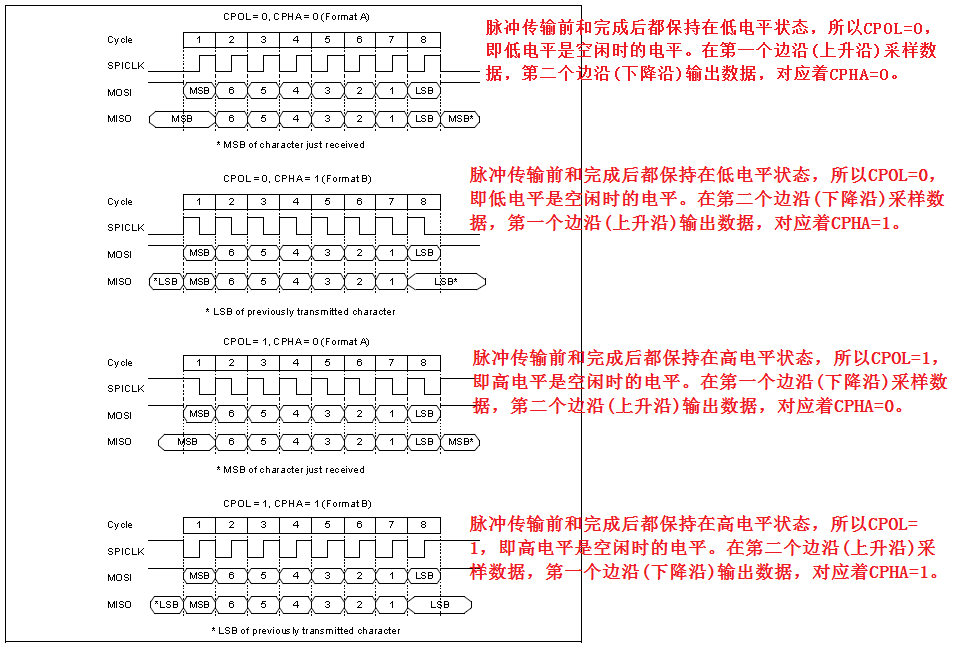

从上图中可以看出,(CPOL=0)的SCK 波形,它有(传输)8 个脉冲,而在脉冲传输前和完成后都保持在【低电平状态】。此时的状态就是时钟的空闲状态或无效状态,因为此时没有脉冲,也就不会有数据传输。同理得出,(CPOL=)1 的图,时钟的空闲状态或无效状态时SCK

是保持【高电平的】。

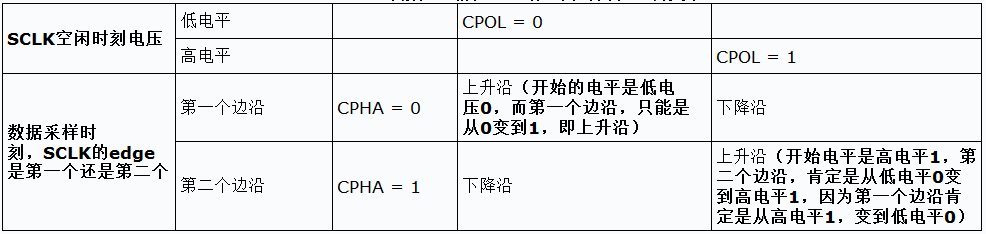

CPHA相位

首先说明一点,capture strobe = latch = read = sample,都是表示数据采样,数据有效的时刻。相位,对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿。

对于:

CPHA=0,表示第一个边沿:

对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿;

CPHA=1,表示第二个边沿:

对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿;

对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿;

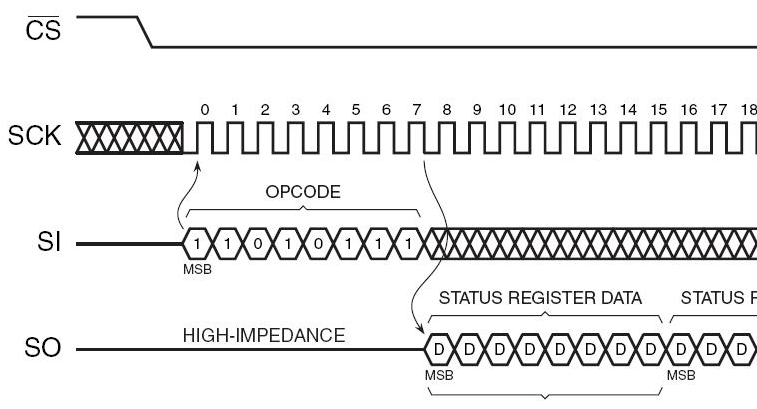

我们看上面的图,发现数据 SI 是对应 SCK 的第一个时钟沿,再仔细看,数据是在SCK的第一个时钟边沿保持稳定【数据被采样捕获】,在下一个边沿改变【SCK 的下降沿数据改变】因此我们得出结论:该系列FLASH 是【数据在第一个时钟沿被采样捕获】或【数据在SPCK 起始边沿捕获,在SPCK 下一个边沿改变】

如何判断CPOL和CPHA

如果起始的SCLK的电平是0,那么CPOL=0,如果是1,那么CPOL=1,然后看数据采样时刻,即时序图数据线上的数据那个矩形区域的中间所对应的位置,对应到上面SCLK时钟的位置,对应着是第一个边沿或是第二个边沿,即CPHA是0或1。(对应的是上升沿还是还是下降沿,要根据对应的CPOL的值,才能确定)。

(1)如何判断CPOL:SCLK的空闲时候的电压,是0还是1,决定了CPOL是0还是1;

(2)如何判断CPHA:而数据采样时刻对应着的SCLK的电平,是第一个边沿还是第二个边沿,对应着CPHA为0还是1。

SCLK的极性,相位,边沿之间的内在逻辑

最后来看一下S3C2440的SPI的CPOL和CPHA,结合前面讲的理论知识,下面的图就很好理解啦!

分享到:

相关推荐

电子-SPI中的极性CPOL和相位CPHA是什么以及如何设置.doc,单片机/嵌入式STM32-F0/F1/F2

介绍了什么是SPI的极性和相位 解释了CPOL和CPHA的内在逻辑关系 阐明软件中间去如何设置极性和相位 并举例说明,如何从数据手册中找到对应内容,来得知对应的极性和相位

在DSP等芯片中有SPI接口,但是通常由于传输模式选择的错误导致连接失败,本文提供了详细的配置方案

SPI(Serial Peripheral Interface)是一种用于串行通信的同步串行数据总线协议,通常用于在微控制器、传感器...多种通信模式: SPI 支持多种通信模式,如时钟极性(CPOL)和相位(CPHA)等,用于确定数据的传输时序。

SPI MODE 2, CPOL = 1, CPHA = 0 (STM32CubeMx, Clock Polarity(CPOL) = High, Clock Phase(CPHA) = 1 Edge, Prescaler(for Baud Rate) = 256) SPI MODE Baud Rate need to less than 1.5MHZ GPIO STM32F103C8T6 : ...

单片机IO模拟四种SPI,模式零CPOL==0&&CPHA;==0 ,模式一_CPOL==1&&_CPHA==0 等

CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性 CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位 SCK = SCLK = SCL = SPI的时钟(Serial Clock) Edge = 边沿,即时钟电平变化的时刻...

SPI主控制器和SPI从控制器仅支持SPI模式0(CPOL = 0,CPHA = 0)! 在硬件中对SPI主控制器和SPI从控制器进行了仿真和测试。 我将GHDL工具用于CI:GitHub Actions环境( )中的自动VHDL模拟。 如果您有任何疑问或...

spi2wb 用SPI总线驱动Wishbone主总线。 协议 如下: 模式b01-> CPOL = 0 CPHA = 1 CS =低电平有效 spi2wb帧的组成如下: 8位模式 写框: MOSI : 1AAAAAAA DDDDDDDD MISO : ZZZZZZZZ ZZZZZZZZ 读框 MOSI : 0AAA...

用VHDL编写的一个SPI主机程序,SPI模块采用最常用的模式0方式(即CPOL=0,CPHA=0)通信。文件内含测试文档,已在Modelsim6.5上测试通过,可在FPGA上直接调用。

由于SCK时钟的相位和极性在不同系统中的配置不尽相同,所以在本设计中通过合理设置CPHA、CPOL和RCV_CPOL的值,达到正确接收数据的目的。 如图所示,两个输入寄存器被用来采样MISO。一个在SCK上升沿采样,另一个在...

全志R40平台的tinav2.1系统下打开SPI2接口 1、(可选修改) Q:\r40_tinav2.1\spi20_r40_tinav2.1\lichee\brandy\build.sh build_uboot() { if [ "x${PLATFORM}" = "xsun50iw1p1" ] || \ [ "x${PLATFORM}" = "xsun...

基于STM32FXXX的软SPI通讯协议,支持多口SPI设计,支持选择8/16位数据宽度 采样沿选择 CPOL CPHA设置,根据从器件所需设置通讯延时。由于STM32FXX硬件SPI在中断服务程序占用时间过程时出现通讯挂死问题,所以编写了...

且SPI的CPOL和CPHA都为0(空闲时低电平 且在第一个变化沿进行采样) 与A121 STM32CubeIDE User Guide中介绍的基本相同 但建议SPI的速度设置为10M以下 并且选择8位数据传输 同时选中软件片选 关闭NSSP

基于单片机ADUC841的spi程序 包括主机和从机的程序 CPHA 和CPOL的介绍

// Mode | Clock Polarity (CPOL/CKP) | Clock Phase (CPHA) // 0 | 0 | 0 // 1 | 0 | 1 // 2 | 1 | 0 // 3 | 1 | 1 -------------------------------------------------------------------------------- // ...

SPI寄存器-Bit 7 – SPIE: 使能SPI 中断 Bit 6 – SPE: 使能SPI接口总线模块 Bit 5 – DORD: 数据次序选择位。...Bit 3 – CPOL: 时钟极性选择位。置1表示SPI总线空闲时SCK为高电平。否则为低电平。

用于软件SPI的内核模块 使用beaglebone balck(内核版本4.19.94-ti-r55)可以使其与SD卡一起使用。 由于它是软件仿真的SPI,... 须藤insmod sw_spi.ko mosi_pin = 69 miso_pin = 68 sck_pin = 66 cpol = 0 cpha = 0

#define CPOL 0x08 //SPCTL.3 #define CPHA 0x04 //SPCTL.2 #define SPDHH 0x00 //CPU_CLK/4 #define SPDH 0x01 //CPU_CLK/16 #define SPDL 0x02 //CPU_CLK/64 #define SPDLL 0x03 //CPU_CLK/128 sfr SPDAT = 0xcf; ...

本人近期学习MPC5606B,硬件环境为TRK-MPC560XB,软件环境codewarrior 10.6,附件中为PCA21125 DSPI DRIVER 的代码. ...CPOL:0 CPHA:0 Receive Interrupt:enable; attention:CONT 欢迎交流,QQ:511437685